# SI/PI Simulation 을 이용한 Test Board 설계

## Design of Test Board Using Signal and Power Integrity Simulation

남승기, 신연숙. 성정우, 김태수, 김성현, 김은정, 조순영, 임영순, 김영부

삼성전자 System LSI 사업부 제품기술팀

[seungki.nam@samsung.com](mailto:seungki.nam@samsung.com)

### Abstract

We demonstrate the procedure of signal integrity (SI) simulation for test board design. For interface between device under test (DUT) and DDR, we apply the demonstrated simulation procedure to probe card design. Therefore, we can save the time and effort to develop customized probe card for the interface.

### I. 서론

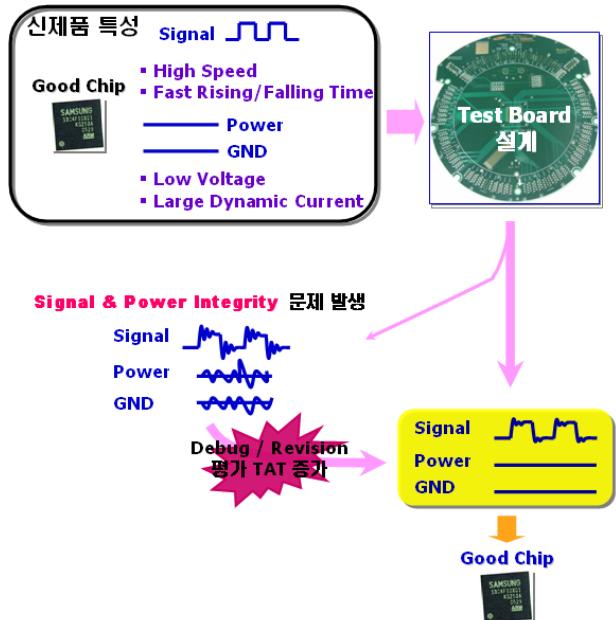

[그림 1]은 제품 평가를 위해 기존에 주로 사용하는 방법을 나타내고 있는데, 지금까지는 제품 평가를 위한 회로가 정해지면, layout 엔지니어가 그 회로를 PCB로 구현하여 설계하고, 제작 후 평가에 적용하면 대부분 원하는 특성을 얻을 수 있었다. 그러나, 최근에 점점 clock speed가 올라가고, rising time이 빨라지며, 동작 전압이 낮아지는 반면, 동작 전류는 커지면서, test board에서의 trace와 via, 그리고 relay 등의 부품들에 의해 발생되는 impedance mismatch, coupling, frequency dependent loss, bandwidth 제한 등으로 인한 signal, power, 및 ground에서의 noise가 제품 평가의 정확성에 많은 영향을 미쳐 board tuning 및 debugging 시간이 증가하고, 최악의 경우는 board를 재 설계하는 경우가 발생하고 있다.

그러나, 다양한 제품에 대한 평가가 필요한 비메모리 사업의 경우에, time-to-market을 실현하기 위해서는 각 제품들이 요구하는 특성을 만족하는 test board를 빠른 시간 내에 설계하여 제품 평가를 할 필요가 있기 때문에, 제작 후 debug 하는 기존의 방식은 더 이상 효율적이지 못하게 되었다. 이러한 이유로, 우리는 최근에 주목 받고 있는 방법인, signal integrity (SI) 및 power integrity (PI) simulation을 test board 설계에 도입하였다.

본 논문에서는, 제작 전 설계된 test board의 특성을 미리 예측하고, board debug 시간을 줄이기 위해 도입한 simulation 방법을 소개하고, 그 효율성을 보여주고자 한다.

[그림 1] 기존의 Test board 특성 확보 방법

### II. 본론

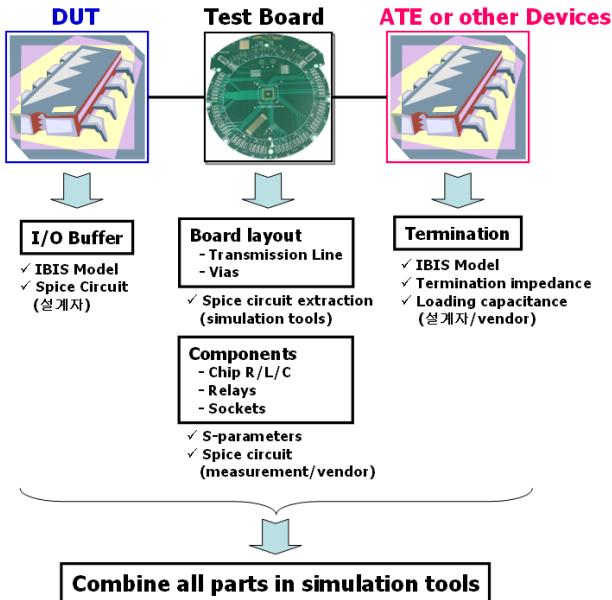

[그림 2]는 test board의 SI 및 PI 특성을 예측하기 위해 필요한 과정을 나타내고 있다. [그림 2]에서 보는 바와 같이, test board는 평가하고자 하는 제품 (DUT), 평가를 위해 필요한 회로 구성 (Test Board) 및 ATE, 세 부분으로 나눌 수 있는데, SI 및 PI 특성을 예측하기 위해서는 각 부분들의 특성을 모델링 해야 한다. 먼저, DUT의 특성은 설계자로부터 I/O buffer에 대한 spice circuit이나 IBIS model을 입수하여 고려하였고, ATE의 특성은 DUT에 신호를 인가하는 경우 PWL로 입력신호의 특성을 기술하고, DUT의 신호를 받는 경우에는 specification에 나와있는 loading capacitance 혹은 termination impedance를 사용하여 고려하였다. Test board의 특성을 나타내기 위해, PCB trace 및 via에 의한 특성을 simulation tool을 사용하여 layout으로부터 spice model을 추출하였으며, relay 등의 부품들은 S-parameter를 측정하여 고려하였다. 마지막으로, [그림 2]에 나타낸

각 부품들의 모델을 결합하여, DUT에서 ATE까지의 전체 특성을 simulation하여 예측하였다.

[그림 2] Simulation을 위해 필요한 모델

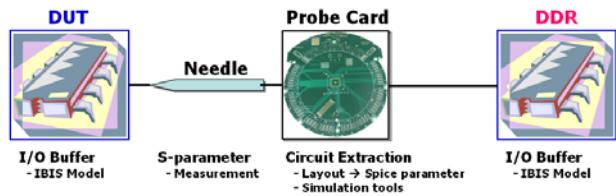

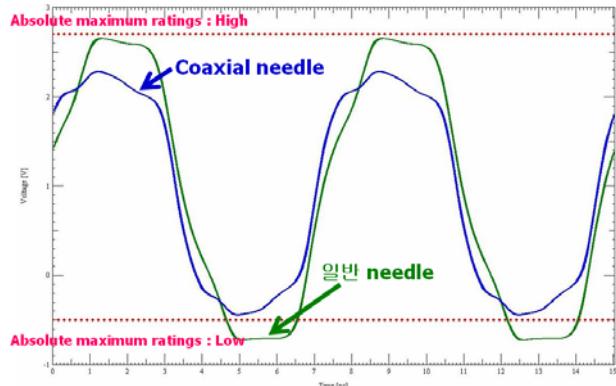

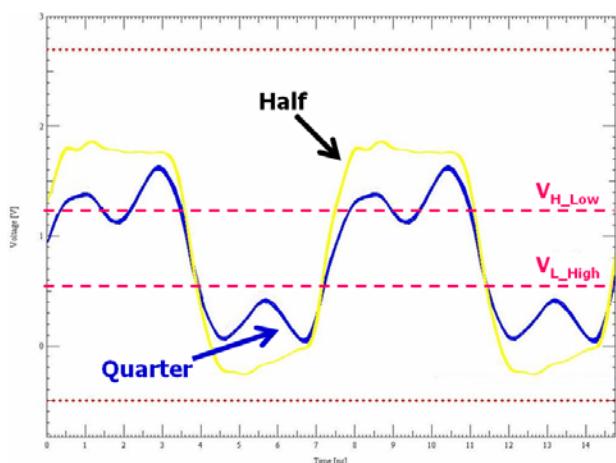

[그림 3]은 도입된 simulation 방식을 사용하여 probe card를 설계한 예를 나타내고 있다. DUT를 wafer에서 평가할 때, DUT와 DDR간의 interface가 원하는 특성을 만족하도록 probe card를 설계하기 위해, SI 특성을 예측하였다. 먼저, DUT의 I/O 특성은 설계자로부터 IBIS model을 입수하여 고려하였고, wafer상의 DUT를 contact하기 위해 사용되는 needle의 특성은 S-parameter를 측정하여 고려하였으며, probe card상의 trace, via 등의 전기적 특성은 Allegro SI tool을 사용하여 spice 회로 형태로 추출하였고, DDR의 I/O 특성은 vendor로부터 IBIS model을 입수하여 고려하였다. 각 부분들의 모델을 Allegro SI tool에서 모두 엮어 test 환경 전체에 대한 SI 특성을 예측하였다. [그림 4]는 cantilever type의 일반 needle을 사용한 경우와, coaxial needle을 사용한 경우에 대한 SI 특성 예측 결과를 나타낸다. [그림 4]에서 보는 바와 같이, 기존의 일반 needle을 사용하는 경우에, impedance mismatch로 인한 overshoot 및 undershoot이 크게 발생하여, DDR specification의 하나인 absolute maximum ratings을 넘어, DDR에 damage를 줄 가능성성이 있는 것으로 예측되었다. 그러나, coaxial needle을 사용한 경우에는 specification을 만족하는 것으로 예측되었다. [그림 5]는 DDR drive-mode에 따른 특성 예측 과정을 나타낸다. [그림 5]에서 보는 바와 같이 quarter

mode인 경우에는 ringback 현상이 나타나 pulse width를 확보할 수 없을 것으로 예측되었고, half mode의 경우에는 pulse width를 확보할 수 있었다 [1]. 각 조건별 probe card를 제작하여 실제 적용하였을 때, coaxial needle을 사용하고, DDR drive-mode가 half mode인 경우에만 vector가 pass되어 simulation에 의한 예측 결과와 일치하였다. 실제 test시에는 quarter mode를 사용하려던 기준의 계획을 바꿔 half mode에 대한 test vector를 입수하여 적용하였다.

[그림 3] Simulation을 활용한 probe card 설계

[그림 4] 일반 needle을 사용한 경우와 coaxial needle을 사용한 경우의 SI 특성 비교

[그림 5] DDR 동작 mode에 따른 SI 특성 비교

### III. 결론

본 논문에서는 적기에 제품 평가에 필요한 특성을 만족하는 test board를 설계하기 위해 도입된 simulation 과정을 설명하였다. 또한 probe card 설계에 적용한 사례를 통해 그 효율성을 보였다. SI simulation을 사용하여 미리 특성을 예측하지 않고 기존의 방법을 그대로 적용하였다면, probe card tuning 및 test PGM debug로 인해 많이 시간이 들어 적기에 제품 평가를 수행하기 어려웠을 것이다. 미리 SI simulation을 수행하여 특성을 예측함으로써 그러한 노력과 시간을 많이 줄여 제품 평가에 크게 이바지할 수 있었다.

### 참고문헌

- [1] Stephen H Hall, et al., “High-Speed Digital System Design”, John Wiley & Sons, Inc., 2000